上个月,三星和豪威这两家公司都表示,他们已经进入了缩小 CMOS 图像芯片像素的下一阶段。总部位于圣克拉拉的Omnivision和韩国三星都声称,其新产品的像素间距仅为 0.56 微米(从一个像素的中心到下一个像素的中心测量),大约与绿光的波长一样大。

三星目前生产0.64 微米像素的图像芯片,Omnivision 在 1 月份发布了0.61 微米传感器。Omnivision 表示,新的 0.56 微米间距的 2亿像素分辨率图像传感器将于今年晚些时候向客户提供,预计2023 年消费者可以在他们的智能手机中找到它们。三星没有透露其传感器何时出现,在 2 月份的IEEE 国际固态电路会议(ISSCC) 上,他们还描述了这项创新。

光通过微透镜进入 CMOS 成像器像素,然后通过滤色器,然后照射到硅光电二极管。在光电二极管中,光导致电荷积累,然后由单独的电路感测并数字化电荷量。使所有这些变小会导致许多潜在的问题。

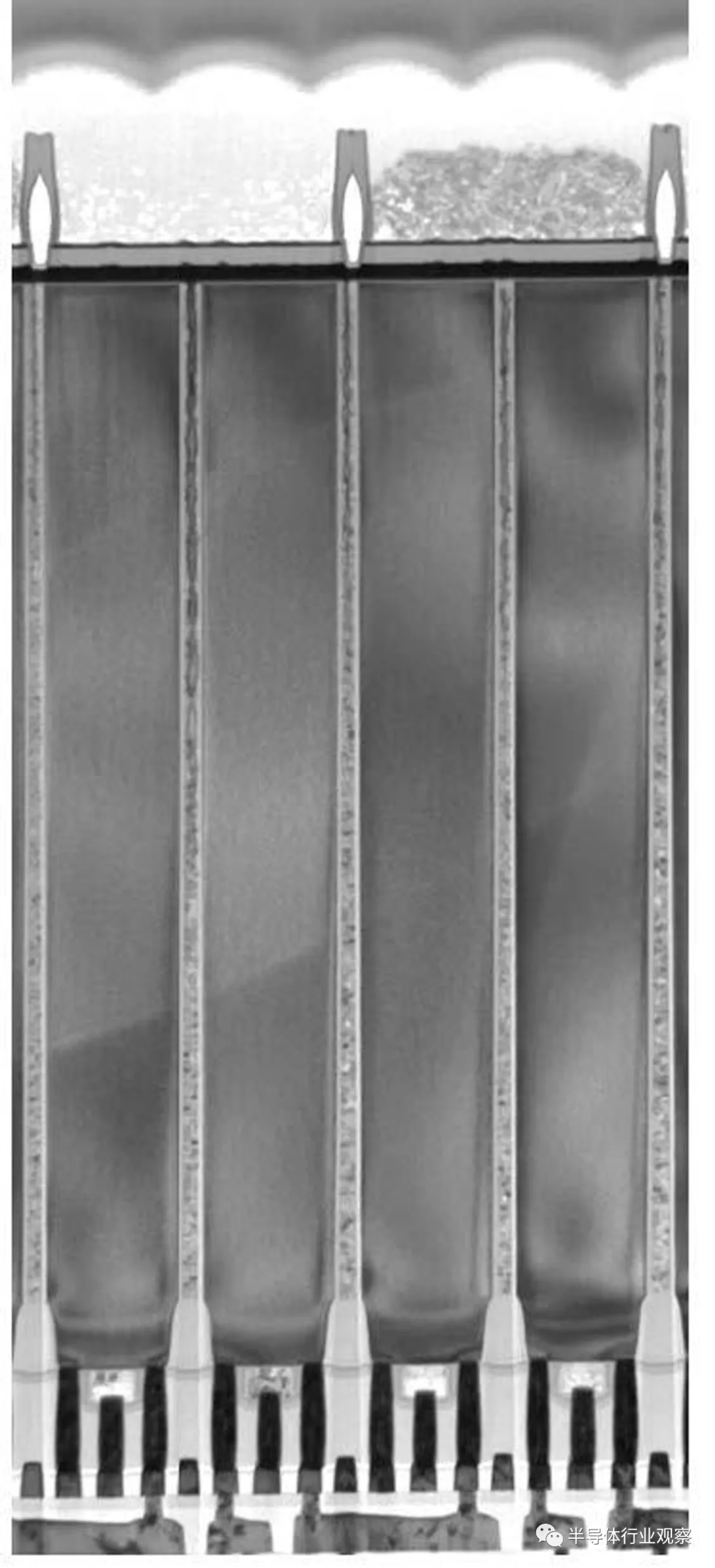

例如,小像素更容易受到串扰的影响,其中与像素呈微小角度进入的光线会通过其相邻像素,从而降低对比度。因此,工程师必须构建能够阻止这种串扰的结构。两家公司都依靠称为深沟槽隔离的技术来实现这一点。也就是说,每个像素的硅与其相邻的硅通过一道一直向下穿过硅的屏障隔开。在像素的顶部,光线进入的地方,他们在硅和像素的集成微透镜之间使用了一个相对较短的电介质“栅栏”。

深沟隔离结构 [长垂直塔] 可防止来自相邻像素的光线进入。金属栅栏 也有助于此。三星通过在每一个之间插入一个空气间隙[亮白色]来提高围栏的能力

为了加强对杂散光的屏障,三星对栅栏进行了修改。考虑到较低折射率的材料可以更好地阻挡光线,三星走到了极端——气隙。三星的 Sungbong Park 告诉 ISSCC 的工程师,Air 在与 CMOS 制造工艺兼容的所有材料中具有最低的折射率。通过沉积和蚀刻工艺,三星工程师在栅栏内制造了一个空气腔,将串扰降低了 1.2%,并将量子效率(光子转化为电子的比率)提高了 7%。

简单地按比例缩小像素的另一个问题是,您可以在它们饱和之前存储更少的电荷,从而限制像素的动态范围。(动态范围是在低光和高光下感知的能力。)Park 说,三星的 0.64 微米设备可以容纳相当于 6000 个电子。在不改变任何东西的情况下将该区域缩小到 0.56 微米,你只剩下 3400 个。三星通过缩小隔离墙和调整光电二极管中掺杂元素的分布来增加体积,使容量恢复到 6000 个电子。

除了缩小深沟隔离屏障之外,三星还改变了其组成。工程师用具有更高介电常数的材料替换了一些绝缘材料,使其在没有光落在像素上时更好地防止电流流动。

两家公司还使用芯片堆叠为像素腾出更多空间。为了被数字处理器解释,每个像素的值必须首先被数字化。曾经,这意味着像素的光电探测部分旁边都有模数转换器电路。但如今,这些电路建立在一个单独的芯片上,该芯片与光电探测器芯片相连,为更多像素留出了空间。然三星拥有自己的图像芯片工厂,但 Ominivision 的电路芯片和光电探测器芯片都依赖台积电。

Park 向工程师保证,未来会有更小的像素。缩小像素“并不容易,但我们会像往常一样找到一种方法,”他说。

豪威方面也表示,公司在实现 0.56μm 超小像素尺寸的同时,还提供高量子效率 (QE) 性能、优异的四相位检测 (QPD) 自动对焦技术和低功耗。这项超小像素技术将会满足多摄像头移动设备对高分辨率和小像素间距图像传感器日益增长的需求。

豪威集团的研发团队证实,在像素尺寸已经小于红光波长的情况下,像素压缩不再受光波长限制。该像素尺寸基于豪威集团的 PureCel? Plus-S 堆叠技术,同时采用了深光电二极管技术将光电二极管精确地嵌入硅片深处。凭借这些先进的技术,豪威集团开发出了超小像素尺寸,在相同的光学格式下可以实现更高的分辨率,并进一步使图像传感器具有更多 ISP 功能、更低的功耗和更高的读取速度。

豪威集团流程工程高级副总裁 Lindsay Grant 说道:“推进像素技术离不开大量的研发创新,尤其是在超越光波长的情况下。虽然芯片尺寸更小了,但是我们并没有牺牲高性能。实际上,在可见光范围内,0.56μm 像素尺寸展示出了与 0.61μm 像素尺寸相当的 QPD 和 QE 性能。”

Grant 补充说:“豪威集团大力投资研发,几乎半数员工都是研发工程师。作为一家全球无晶圆厂半导体提供商,我们还与代工厂合作伙伴开发新工艺技术方法,实现业界领先创新。这是一个引人注目的成就,我们优秀的研发团队以及我们的代工厂合作伙伴能够持续引领像素压缩,我对他们表示赞赏。”